# **CCS Technical Documentation NPM-8 Series Transceivers**

## 3. System Module

Issue 1 07/2002 ©Nokia Corporation

#### **Contents**

|                                               | age N |

|-----------------------------------------------|-------|

| Transceiver NPM-8                             |       |

| Introduction                                  |       |

| Hardware characteristics                      |       |

| Technical Summary                             |       |

| Technical Specifications                      |       |

| Internal Signals and Connections              |       |

| External Signals and Connections              |       |

| Functional Description                        |       |

| Modes of Operation                            |       |

| Charger Detection                             |       |

| Charge Control                                |       |

| Supported Chargers                            |       |

| Charger Interface Protection                  |       |

| Charging Circuitry Electrical Characteristics |       |

| Power Up and Reset                            |       |

| A/D Channels                                  |       |

| LCD & Keyboard Backlight                      |       |

| LCD cell                                      |       |

| SIM Interface                                 |       |

| Internal Audio                                |       |

| Internal Microphone                           | 28    |

| Ringer                                        |       |

| Accessories                                   | 29    |

| External Audio                                | 29    |

| Analog Audio Accessory Detection              |       |

| Headset Detection                             |       |

| PPH-1 Detection                               |       |

| DC-OUT Interface                              | 32    |

| Implementation                                | 32    |

| Keyboard                                      | 33    |

| RF Interface Block                            | 33    |

| Memory Module                                 | 33    |

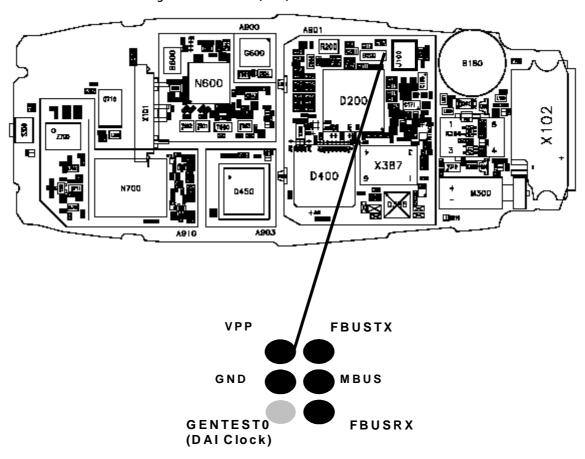

| Test Interfaces                               | .34   |

| Service Interface                             | 35    |

| RF Module                                     | .35   |

| Environmental specifications                  | 35    |

| Main technical specifications                 | 35    |

| RF frequency plan                             | 37    |

| DC characteristics                            |       |

| Typical current consumption                   | 38    |

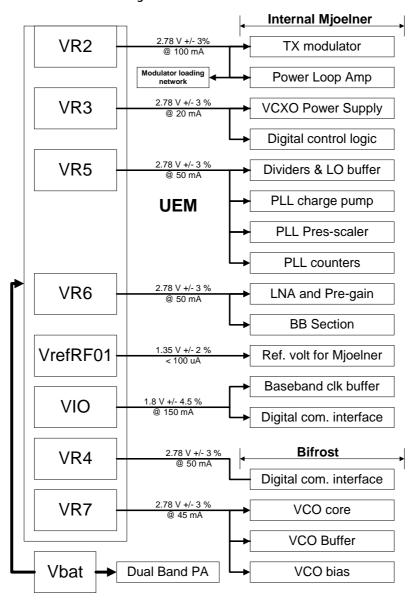

| Power distribution diagram                    |       |

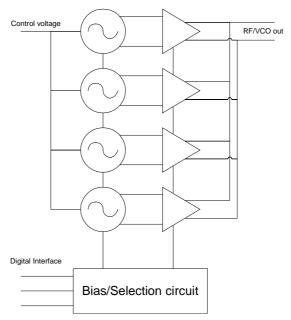

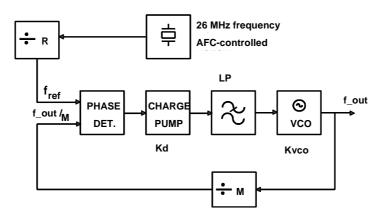

| Frequency synthesizers                        | 39    |

| Receiver                                      |       |

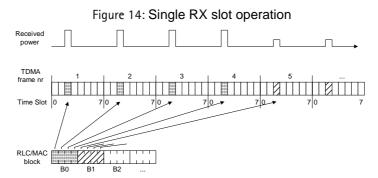

| GPRS Requirements                             |       |

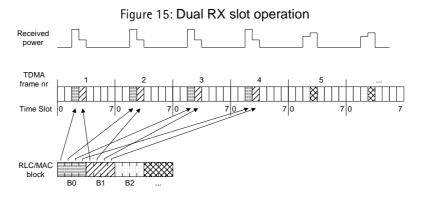

| GPRS Dual Slot                                |       |

| TX                                            |       |

| Synthesizer                                   |       |

## **CCS Technical Documentation**

| RF Characteristics                 | 44 |

|------------------------------------|----|

| Channel numbers and frequencies    |    |

| Main RF characteristics            |    |

| Transmitter characteristics        | 44 |

| Output power requirements GSM850   | 45 |

| Output power requirements, GSM1900 | 45 |

| Receiver characteristics           | 46 |

## Transceiver NPM-8

#### Introduction

This section specifies the baseband module for the NPM-8 transceiver. The baseband module includes the baseband engine chipset, the UI components, and the acoustical parts for the transceiver.

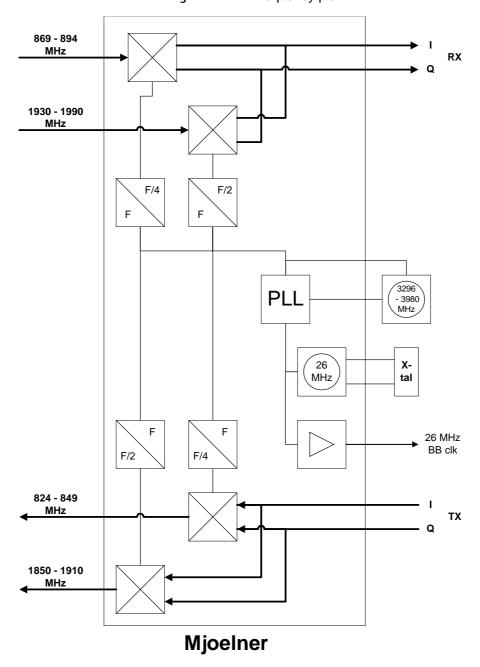

NPM-8 is a handportable, dualband GSM 850/1900 phone, with GPRS for the Basic/ Expression segment, using DCT4 generation baseband (UEM/UPP) and RF (MJOELNER) circuitry.

NPM-8 supports both three- and two-wire type DCT3 chargers. Three-wire chargers are treated like two-wire types. There is no separate PWM output; the third wire is connected to ground.

The BLC-1 Li-ion battery is used as the main power source for NPM-8. The BLC-1 has a nominal capacity of 825 MAh.

#### Hardware characteristics

- Hi-Res (96x65) illuminated B&W display

- ESD-proof keymat

- Support for internal semi-fixed batteries (Janette type)

- Audio amplifier and SALT speaker for MIDI support

- Internal vibra

- Supports voice dial activation via headset button

- DC out feature for supporting electrical A-covers

- Support for both Li-ion and NiMH batteries

Note: 5V SIM cards are no longer supported by DCT-4 generation baseband.

#### **Technical Summary**

The baseband module contains two main ASICs (UEM and UPP). The baseband module also contains an audio amplifier for MIDI support and a 64-Mbit Flash IC. The baseband is based on the DCT4 engine program.

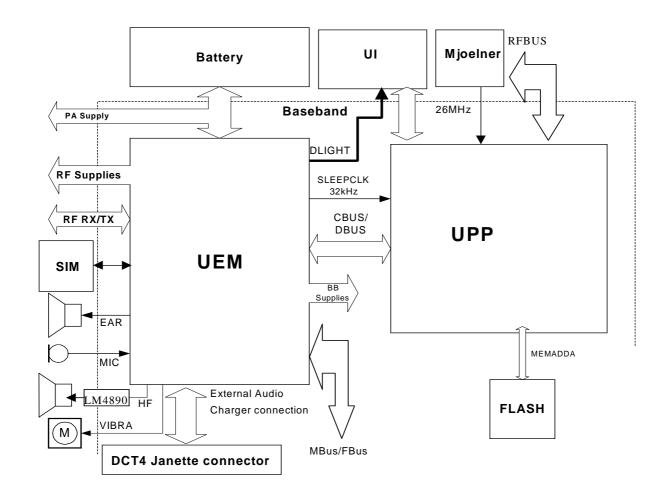

Figure 1: NPM-8 baseband block diagram

The UEM supplies both the baseband module as well as the RF module with a series of voltage regulators. Both the RF and Baseband modules are supplied with regulated voltages of 2.78V and 1.8V. The UEM includes six linear LDO (low drop out) regulators for baseband and seven regulators for RF, the BB regulator VFLASH1, RF regulators VR1B, VR4 as well as the current sources (IPA1 and IPA2 must be kept disabled by SW as they are left disconnected on the PWB). The UEM also supplies the baseband SIM interface with a programmable voltage of either 1.8V or 3.0V. The UPP core is supplied with a programmable voltage of 1.0V, 1.3V, 1.5V, or 1.8V.

The UPP operates from a 26MHz clock, coming from the RF ASIC Mjoelner. The 26 MHz clock is internally divided by two, to the nominal system clock of 13 MHz.

The UEM contains a real-time clock, developed from the 32.768 MHz crystal oscillator. The 32.768 MHz clock is fed to the UPP as a sleep clock.

The communication between the UEM and the UPP is done via the bidirectional serial busses, CBUS and DBUS. The CBUS is controlled by the MCU and operates at a speed of 1 MHz. The DBUS is controlled by the DSP and operates at a speed of 13 MHz. Both processors are located in the UPP.

The interface between the baseband and the RF section is mainly handled by the UEM

ASIC. UEM provides A/D and D/A conversion of the in-phase and quadrature receive and transmit signals and also A/D and D/A conversions of received and transmitted audio signals to and from the user interface. The UEM supplies the analog signals to the RF section according to the UPP DSP digital control. The RF ASIC Mjoelner is controlled through UPP RFBUS serial interface. There also are the separate signals for PDM-coded audio. Digital speech processing is handled by the DSP inside the UPP ASIC. The UEM ASIC is a dual-voltage circuit supplying the digital section with 1.8 V and the analog section with

The baseband supports both internal and external microphone inputs and speaker outputs. Input and output signal source selection and gain control is handled by the UEM according to control messages from the UPP. Keypad tones, DTMF, and other audio tones are generated and encoded by the UPP and transmitted to the UEM for decoding. NPM-8 has two external control interfaces: FBUS and MBUS. The serial control interfaces can be accessed through the test pads located in the battery area.

#### **Technical Specifications**

Operating conditions - Temperature Conditions

2.78 V. VBAT is also used in some blocks.

Table 1: Temperature conditions for NPM-8

| Environmental conditions | Ambient temperature              |

|--------------------------|----------------------------------|

| Normal operation         | -25° C +55° C                    |

| Reduced performance      | -40° C25° C<br>and +55° C +85° C |

#### Absolute Maximum Ratings

Table 2: Absolute maximum ratings

| Signal                | Rating    |

|-----------------------|-----------|

| Battery voltage       | -0.3 5.4V |

| Charger input voltage | -0.3 20V  |

#### DC Characteristics

Regulators and Supply Voltage Ranges

Table 3: Battery voltage range

| Signal | Min   | Nom   | Max     | Note             |

|--------|-------|-------|---------|------------------|

| VBAT   | 3.1 V | 3.6 V | 4.235 V | 3.1 V SW cut off |

| Signal  | Min                                    | Nom                                | Max                                      | Note                                                                                                           |

|---------|----------------------------------------|------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| VANA    | 2.70 V                                 | 2.78 V                             | 2.86 V                                   | $I_{max} = 80 \text{ mA}$                                                                                      |

| VFLASH1 | 2.70 V                                 | 2.78 V                             | 2.86 V                                   | $I_{max} = 70 \text{ mA}$<br>$I_{Sleep} = 1.5 \text{ mA}$                                                      |

| VFLASH2 | 2.70 V                                 | 2.78 V                             | 2.86 V                                   | Not used                                                                                                       |

| VSIM    | 1.745 V<br>2.91 V                      | 1.8 V<br>3.0 V                     | 1.855 V<br>3.09 V                        | $I_{max} = 25 \text{ mA}$<br>$I_{Sleep} = 0.5 \text{ mA}$                                                      |

| VIO     | 1.72 V                                 | 1.8 V                              | 1.88 V                                   | $I_{max} = 150 \text{ mA}$<br>$I_{Sleep} = 0.5 \text{ mA}$                                                     |

| VCORE   | 1.0 V<br>1.235 V<br>1.425 V<br>1.710 V | 1.053 V<br>1.3 V<br>1.5 V<br>1.8 V | 1.106 V<br>1.365 V<br>1.575 V<br>1.890 V | I <sub>max</sub> = 200 mA<br>I <sub>Sleep</sub> = 0.2 mA<br>Used voltages:<br>(c015) = 1.8 V<br>(c035) = 1.5 V |

Table 5: RF regulators

| Signal | Min              | Nom             | Max              | Note                                                      |

|--------|------------------|-----------------|------------------|-----------------------------------------------------------|

| VR1A   | 4.6 V            | 4.75 V          | 4.9 V            | $I_{max} = 10 \text{ mA}$                                 |

| VR1A   | 4.6 V            | 4.75 V          | 4.9 V            | Not used                                                  |

| VR2    | 2.70 V<br>3.20 V | 2.78 V<br>3.3 V | 2.86 V<br>3.40 V | I <sub>max</sub> = 100 mA                                 |

| VR3    | 2.70 V           | 2.78 V          | 2.86 V           | I <sub>max</sub> = 20 mA                                  |

| VR4    | 2.70 V           | 2.78 V          | 2.86 V           | Not used                                                  |

| VR5    | 2.70 V           | 2.78 V          | 2.86 V           | $I_{max} = 50 \text{ mA}$<br>$I_{Sleep} = 0.1 \text{ mA}$ |

| VR6    | 2.70 V           | 2.78 V          | 2.86 V           | $I_{max} = 50 \text{ mA}$<br>$I_{Sleep} = 0.1 \text{ mA}$ |

| VR7    | 2.70 V           | 2.78 V          | 2.86 V           | I <sub>max</sub> = 45 mA                                  |

**Table 6: Current sources**

| Signal        | Min  | Nom | Max  | Note     |

|---------------|------|-----|------|----------|

| IPA1 and IPA2 | 0 mA | -   | 5 mA | Not used |

## **Internal Signals and Connections**

The following tables describe internal signals. The signal names can be found on the schematic for the EN9 PWB.

#### **Audio**

NOKIA

Table 7: Internal microphone

| Signal                       | Min   | Nom   | Max                  | Condition | Note                                          |

|------------------------------|-------|-------|----------------------|-----------|-----------------------------------------------|

| MIC1P (Differential input P) | -     | -     | 100 mV <sub>pp</sub> | G=20 dB   | 1kΩ to MIC1B<br>(RC filtered by<br>470R/22uF) |

| MIC1N (Differential input N) | -     | -     | 100 mV <sub>pp</sub> | G=20 dB   | 1k $\Omega$ to GND                            |

| MIC1B (Microphone Bias)      | 2.0 V | 2.1 V | 2.25 V               | DC        |                                               |

| External loading of MICB1    | -     | -     | 600 uA               | DC        |                                               |

Table 8: Internal speaker (Differential output EARP & EARN)

| Signal                          | Min | Nom | Max | Condition | Note                |

|---------------------------------|-----|-----|-----|-----------|---------------------|

| Output voltage swing            | 4.0 | -   | -   | Vpp       | Differential output |

| Load Resistance (EARP to EARN)  | 26  | 32  | -   | W         |                     |

| Load Capacitance (EARP to EARN) | -   | -   | 50  | nF        |                     |

#### MIDI

Table 9: Connections between UPP and LM4890

| Signal   | From      | То       | Parameter  | Min | Max   | Unit | Notes                                        |

|----------|-----------|----------|------------|-----|-------|------|----------------------------------------------|

| Shutdown | GENIO[14] | Shutdown | Vih<br>Vil | 1.2 | - 0.4 | V    | LM4890<br>detections<br>thresholds<br>levels |

Table 10: Connections between UEM/Battery and LM4890

| Signal name                    | From                                                                 | То     | Parameter    | Min | Max | Unit | Notes                                             |

|--------------------------------|----------------------------------------------------------------------|--------|--------------|-----|-----|------|---------------------------------------------------|

| XAUDIO[1] Fil-<br>tered signal | UEM, HF No<br>direct con-<br>nection<br>between<br>UEM and<br>LM4890 | LM4890 | Output Swing | 1.0 | -   | Vpp  | with 60 dB<br>signal to total<br>distortion ratio |

| VBAT                           | Battery                                                              | LM4890 | Supply       | 3.1 | 4.2 | V    | Lower limit is<br>SW cut-off                      |

## LCD

Table 11: LCD connector interface

| Pin | Signal            | NMP<br>net | Symbol            | Parameter                                     | Min.                   | Ty<br>p. | Max.                   | Un<br>it | Notes                                  |

|-----|-------------------|------------|-------------------|-----------------------------------------------|------------------------|----------|------------------------|----------|----------------------------------------|

| 1   | /RES              | XRES       |                   | Reset                                         | -                      | -        | 0.3 x V <sub>DDI</sub> | V        | Logic Low,<br>active                   |

|     |                   |            | t <sub>rw</sub>   |                                               | 1000                   | -        | -                      | ns       | For valid reset                        |

| 2   | /SCE              | XCS        |                   | Chip Select                                   | 0.7 x V <sub>DDI</sub> | -        | -                      | V        | Logic High                             |

|     |                   |            |                   |                                               | -                      | -        | 0.3 x V <sub>DDI</sub> | V        | Logic Low,<br>active                   |

|     |                   |            | t <sub>S2</sub>   |                                               | 60                     | -        | -                      | ns       | Setup time                             |

|     |                   |            | t <sub>H2</sub>   |                                               | 100                    | -        | -                      | ns       | Hold time                              |

| 3   | VSS               | VSS        | GND               | Ground                                        | -                      | 0        | -                      | V        |                                        |

| 4   | SDATA             | SDA        |                   | Input                                         | 0.7 x V <sub>DDI</sub> | -        | -                      | V        | Logic High                             |

|     |                   |            |                   |                                               | -                      | -        | 0.3 x V <sub>DDI</sub> | V        | Logic Low                              |

|     |                   |            |                   | Output @ $I_{OL} = 0.5mA$ , $I_{OH} = -0.5mA$ | 0.7 x V <sub>DDI</sub> | -        | -                      | V        | Logic High                             |

|     |                   |            |                   |                                               | -                      | -        | 0.3 x V <sub>DDI</sub> | V        | Logic Low                              |

|     |                   |            | t <sub>s1</sub>   |                                               | 100                    | -        | -                      | ns       | Data setup time                        |

|     |                   |            | t <sub>H1</sub>   |                                               | 100                    | -        | -                      | ns       | Data hold time                         |

| 5   | SCLK              | SCLK       |                   | Serial clock input                            | 0.7 x V <sub>DDI</sub> | _        | -                      | V        | Logic High                             |

|     |                   |            |                   |                                               | -                      | -        | 0.3 x V <sub>DDI</sub> | V        | Logic Low                              |

|     |                   |            | t <sub>cyc</sub>  |                                               | 153,8                  | -        | -                      | ns       | Serial clock<br>cycle (max. 4<br>MHz)  |

|     |                   |            | t <sub>PWH1</sub> |                                               | 50                     | _        | -                      | ns       | Serial clock high pulse width          |

|     |                   |            | t <sub>PWL1</sub> |                                               | 50                     | -        | -                      | ns       | Serial clock low pulse width           |

| 6   | VDD <sub>1</sub>  | VDDI       |                   | VDD digital power supply                      | 1.72                   | 1.8      | 1.88                   | V        |                                        |

| 7   | VDD <sub>2i</sub> | VDD        |                   | Booster<br>power supply                       | 2.6                    | 2.7<br>8 | 2.86                   | V        | VFLASH1                                |

| 8   | VLCD-<br>out      | VOUT       |                   | Booster out-<br>put                           | -                      | -        | 12                     | V        | Decoupled to<br>GND on PCB<br>with 1uF |

## **CCS Technical Documentation**

#### Baseband – RF interface

Table 12: BB - RF interface description

| Signal name     | From | То     | Parameter                         | Min.     | Тур.    | Max.      | Unit | Notes                                                  |

|-----------------|------|--------|-----------------------------------|----------|---------|-----------|------|--------------------------------------------------------|

| RFICCNTRL (2:0) |      |        | MJOELNER/BIFRO                    | OST cont | rol bus | •         |      |                                                        |

| RFBUSEN1X       | UPP  | MJOEL- | Logic "1"                         | 1.38     | -       | 1.80      | V    | RF Chip select                                         |

|                 |      | NER    | Logic "0"                         | 0        | -       | 0.4       | V    |                                                        |

| RFBUSDA         | UPP  | MJOEL- | Logic "1"                         | 1.38     | -       | 1.80      | V    | RF serial                                              |

|                 |      | NER    | Logic "0"                         | 0        | -       | 0.4       | V    | control bus<br>(bi-directional)                        |

| RFBUSCLK        | UPP  | MJOEL- | Logic "1"                         | 1.38     | -       | 1.80      | V    | RF bus clock                                           |

|                 |      | NER    | Logic "0"                         | 0        | -       | 0.4       | V    |                                                        |

| Clock           |      |        | System clock for                  | phone    |         |           |      |                                                        |

| RFCLK           | MJOE | UPP    | Frequency                         | -        | 26      | -         | MHz  | System clock                                           |

|                 | LNER |        | Signal ampli-<br>tude             | 0.3      | 1       | 1.37<br>6 | Vpp  | UPP minimum rec-<br>ommended ampli-<br>tude is 0.3Vpp. |

|                 |      |        | Duty cycle<br>(Mjoelner<br>spec.) | 40       | -       | 60        | 0/0  | Waveform: Sinus/<br>triangle                           |

| RFCONV (9:0)    |      |        | RF / BB analogue                  | signals  |         |           |      |                                                        |

| RXIINP          | MJOE |        | Voltage swing                     | 1.35     | 1.4     | 1.45      | V    | Positive in-phase                                      |

|                 | LNER |        | DC level                          | 1.3      | 1.35    | 1.4       | V    | Rx signal                                              |

|                 |      |        | I/Q amplitude<br>mismatch         | -        | -       | 0.2       | dB   |                                                        |

|                 |      |        | I/Q phase mis-<br>match           | -5       | -       | 5         | Deg. |                                                        |

|                 |      |        | Data clock rate                   | -        | -       | 13        | MHz  |                                                        |

| RXIINN          | MJOE | UEM    | Voltage swing                     | 1.35     | 1.4     | 1.45      | V    | Negative in-phase                                      |

|                 | LNER |        | DC level                          | 1.3      | 1.35    | 1.4       | V    | Rx signal                                              |

|                 |      |        | I/Q amplitude<br>mismatch         | -        | -       | 0.2       | DB   |                                                        |

|                 |      |        | I/Q phase mis-<br>match           | -5       | -       | 5         | Deg. |                                                        |

|                 |      |        | Data clock rate                   | -        | -       | 13        | MHz  |                                                        |

| RXQINP  | MJOE | UEM           | Voltage swing              | 1.35 | 1.4  | 1.45 | V    | Positive quadra-                      |

|---------|------|---------------|----------------------------|------|------|------|------|---------------------------------------|

|         | LNER |               | DC level                   | 1.3  | 1.35 | 1.4  | V    | ture phase RX sig-<br>nal             |

|         |      |               | I/Q amplitude<br>mismatch  | -    | -    | 0.2  | dB   |                                       |

|         |      |               | I/Q phase mis-<br>match    | -5   | -    | 5    | Deg. |                                       |

|         |      |               | Data clock rate            | -    | -    | 13   | MHz  |                                       |

| RXQINN  | MJOE | UEM           | Voltage swing              | 1.35 | 1.4  | 1.45 | ٧    | Negative quadra-                      |

|         | LNER |               | DC level                   | 1.3  | 1.35 | 1.4  | ٧    | ture phase RX sig-<br>nal             |

|         |      |               | I/Q amplitude<br>mismatch  | -    | -    | 0.2  | dB   |                                       |

|         |      |               | I/Q phase mis-<br>match    | -5   | -    | 5    | Deg. |                                       |

|         |      |               | Data clock rate            | -    | -    | 13   | MHz  |                                       |

| TXIOUTP | UEM  | MJOEL-<br>NER | Diff. Voltage<br>swing     | 2.15 | 2.2  | 2.25 | Vpp  | Positive TX signal (program-able      |

|         |      |               | DC level                   | 1.10 | 1.20 | 1.25 | ٧    | voltage swing)                        |

|         |      |               | Source imped-<br>ance      | -    | -    | 200  | W    |                                       |

|         |      |               | Data clock rate            | -    | -    | 13   | MHz  |                                       |

| TXIOUTN | UEM  | MJOEL-<br>NER | Differential voltage swing | 2.15 | 2.2  | 2.25 | Vpp  | Negative TX sig-<br>nal (program-able |

|         |      |               | DC level                   | 1.17 | 1.20 | 1.23 | ٧    | voltage swing)                        |

|         |      |               | Source imped-<br>ance      | -    | -    | 200  | W    |                                       |

|         |      |               | Data clock rate            | -    | -    | 13   | MHz  |                                       |

| TXQOUTP | UEM  | MJOEL-<br>NER | Differential voltage swing | 2.15 | 2.2  | 2.25 | Vpp  | Positive TX signal (program-able      |

|         |      |               | DC level                   | 1.17 | 1.20 | 1.23 | V    | voltage swing)                        |

|         |      |               | Source imped-<br>ance      | -    | -    | 200  | W    |                                       |

|         |      |               | Data clock rate            | -    | -    | 13   | MHz  |                                       |

| TXQOUTN | UEM  | MJOEL-<br>NER | Differential voltage swing | 2.15 | 2.2  | 2.25 | Vpp  | Negative TX sig-<br>nal (program-able |

|         |      |               | DC level                   | 1.17 | 1.20 | 1.23 | V    | voltage swing)                        |

|         |      |               | Source imped-<br>ance      | -    | -    | 200  | W    |                                       |

|         |      |               | Data clock rate            | -    | -    | 13   | MHz  | ]                                     |

## **CCS Technical Documentation**

| GENIO (28:0)       |              |               | General purpose                  | 1/0       |      |           |      |                                                        |  |

|--------------------|--------------|---------------|----------------------------------|-----------|------|-----------|------|--------------------------------------------------------|--|

| GENIO5             | UPP          | MJOEL-        | Logic "1"                        | 1.38      | -    | 1.80      | V    | Transmitter power                                      |  |

| (TXP)              |              | NER           | Logic "0"                        | 0         | -    | 0.4       | V    | control enable                                         |  |

| GENIO6             | UPP          | MJOEL-        | Logic "1"                        | 1.38      | -    | 1.80      | V    | Reset to RF chip                                       |  |

| (RESETX_MJO<br>EL) |              | NER           | Logic "0"                        | 0         | -    | 0.4       | V    |                                                        |  |

| RFAUXCONV(2:       | 0)           |               | RF / BB analogue control signals |           |      |           |      |                                                        |  |

| AUXOUT             | UEM          | MJOEL-        | Output voltage                   | 0.12      | -    | 2.50      | V    | Transmitter power                                      |  |

|                    |              | NER           | Source imped-<br>ance            | -         | -    | 200       | W    | control                                                |  |

|                    |              |               | Resolution                       | -         | 10   | -         | Bits |                                                        |  |

| Regulators         | Regulators   |               |                                  |           |      |           |      |                                                        |  |

| VBAT<br>(VBATREGS) | Bat-<br>tery | PA / UEM      | Output voltage                   | 2.9       | 3.6  | 4.2       | V    | Battery cut-off is set by UEM to 2.9 V                 |  |

| VR2                | UEM MJOEL-   |               | Output voltage                   | 2.64      | 2.78 | 2.86      | V    | Supply to :                                            |  |

|                    |              | NER           | Current                          | 0.1       | -    | 100       | mA   | TX – chain, Power<br>Loop Control and<br>Digital logic |  |

| VR3                | UEM          | MJOEL-        | Output voltage                   | 2.64      | 2.78 | 2.86      | V    | Supply to :                                            |  |

|                    |              | NER           | Current                          | 0.1       | -    | 20        | mA   | Ref. Osc.                                              |  |

| VR5                | UEM          | MJOEL-        | Output voltage                   | 2.64      | 2.78 | 2.86      | V    | Supply to :                                            |  |

|                    |              | NER           | Current                          | 0.1       | -    | 50        | mA   | PLL, Divider, LO<br>buffers                            |  |

| VR6                | UEM          | MJOEL-        | Output voltage                   | 2.64      | 2.78 | 2.86      | V    | Supply to :                                            |  |

|                    |              | NER           | Current                          | 0.1       | -    | 50        | mA   | LNA's, Pregain                                         |  |

| VR7                | UEM          | VCO           | Output voltage                   | 2.64      | 2.78 | 2.86      | V    | Supply to :                                            |  |

|                    |              |               | Current                          | 0.1       | -    | 45        | mA   | LO buffers, Local oscillators                          |  |

| VREFRF01           | UEM          | MJOEL-<br>NER | Output voltage                   | 1.33<br>4 | 1.35 | 1.36<br>6 | V    | Used in MJOELNER<br>(VBEXT) as 1.35V                   |  |

|                    |              |               | Current                          | -         | -    | 100       | μΑ   | reference                                              |  |

|                    |              |               | Current                          | -         | -    | 100       | μΑ   |                                                        |  |

| VI0                | UEM          | MJOEL-        | Output voltage                   | 1.71      | 1.8  | 1.88      | V    | Supply to :                                            |  |

|                    | NER          |               | Current                          | 0.1       | -    | 150       | mA   | BB buffer                                              |  |

Table 13: Board clocks

| Signal name | From     | То  | Min | Тур | Max | Unit | Notes |

|-------------|----------|-----|-----|-----|-----|------|-------|

| RFCLK       | MJOELNER | UPP | -   | 26  | -   | MHz  |       |

Table 13: Board clocks

| Signal name | From      | То       | Min | Тур           | Max | Unit | Notes                                |

|-------------|-----------|----------|-----|---------------|-----|------|--------------------------------------|

| SLEEPCLK    | UEM       | UPP      | -   | 32.768        | -   | kHz  |                                      |

| RFCONVCLK   | UPP       | UEM      |     | 13            | -   | MHz  | Active when RF converters are active |

| RFBUSCLK    | UPP       | MJOELNER | -   | 13            | 13  | MHz  | Only active when busenable is active |

| DBUSCLK     | UPP (DSP) | UEM      | -   | 13            | 13  | MHz  | Only active when busenable is active |

| CBUSCLK     | UPP (MCU) | UEM      | -   | 1             | 1   | MHz  | Only active when busenable is active |

| LCDCAMCLK   | UPP       | LCD      | 0.3 | 3.25<br>0.650 | 4   | MHz  | Only active when busenable is active |

## **External Signals and Connections**

System connector (X102)

Table 14: DC connector

| Pin | Signal | Min                     | Nom                   | Max                                                                     | Condition                      | Note                   |

|-----|--------|-------------------------|-----------------------|-------------------------------------------------------------------------|--------------------------------|------------------------|

| 2   | VCHAR  | -                       | 11.1V <sub>peak</sub> | 16.9 V <sub>peak</sub><br>7.9 V <sub>RMS</sub><br>1.0 A <sub>peak</sub> | Standard<br>charger<br>(ACP-7) | Charger positive input |

|     |        | 7.0<br>V <sub>RMS</sub> | 8.4 V <sub>RMS</sub>  | 9.2 V <sub>RMS</sub><br>850 mA                                          | Fast<br>charger                |                        |

| 1   | CHGND  | -                       | 0                     | -                                                                       |                                | Charger ground         |

Table 15: External microphone

| Signal                       | Min   | Nom   | Max                 | Condition | Note               |

|------------------------------|-------|-------|---------------------|-----------|--------------------|

| MIC2P (Differential input P) | -     | -     | 100mV <sub>pp</sub> | G=20dB    | 1kΩ to MIC1B       |

| MIC2N (Differential input N) | -     | -     | 100mV <sub>pp</sub> | G=20dB    | 1k $\Omega$ to GND |

| MIC2B (Microphone Bias)      | 2.0 V | 2.1 V | 2.25 V              | DC        | Unloaded           |

| External loading of MICB2    | -     | -     | 600 uA              | DC        |                    |

Table 16: External speaker, differential output XEARP(HF) & XEARN (HFCM)

| Signal                      | Min | Nom | Max | Units | Note                                                             |

|-----------------------------|-----|-----|-----|-------|------------------------------------------------------------------|

| Output voltage swing*       | 2.0 | -   | -   | Vpp   | Differential output, with 60 dB signal to total distortion ratio |

| * seen from transducer side |     |     |     |       |                                                                  |

**NOKIA**

| Signal                                               | Min  | Nom | Max  | Units | Note |

|------------------------------------------------------|------|-----|------|-------|------|

| Common voltage level for HF output (HF & HFCM) VCMHF | 0.75 | 0.8 | 0.85 | V     |      |

| Load resistance (HF to HFCM)                         | 30   | -   | -    | W     |      |

| Load capacitance (HF to HFCM)                        | -    | -   | 10   | nF    |      |

Table 17: Headset detection

| Signal  | Min | Nom | Max              | Condition | Note                                                           |

|---------|-----|-----|------------------|-----------|----------------------------------------------------------------|

| HookInt | 0 V | -   | 2.86 V<br>(VANA) |           | Headset button call control, con-<br>nected to UEMAD-converter |

| HeadInt | 0 V | -   | 2.86 V<br>(VANA) |           | Accessory detection, connected to UEMAD-converter              |

DC-OUT (J307,J308 and J309)

Table 18: DC-OUT Connections

| Pad  | Name           | Parameter       | Min  | Тур | Max  | Unit | Notes             |

|------|----------------|-----------------|------|-----|------|------|-------------------|

| J307 | Power          | Voltage (open)  | -    | -   | Vbat | V    | Output power line |

|      |                | Current (short) | 56   | 64  | 72   | mA   |                   |

| J308 | CTI<br>(Input) | Resistor value  | 30.9 | -   | 750  | kΩ   | Cover detection   |

| J309 | GND            | -               | -    | -   | -    | -    | Ground            |

#### SIM (X387)

3. System Module

Table 19: SIM Connector

| Pin | Name | Parameter            | Min       | Тур        | Max          | Unit | Notes                                         |

|-----|------|----------------------|-----------|------------|--------------|------|-----------------------------------------------|

| 1   | CLK  | Frequency            | -         | 3.25       | -            | MHz  | SIM clock                                     |

|     |      | Trise/Tfall          | -         | -          | 50           | ns   |                                               |

| 2   | RST  | 1.8V SIM<br>Card     | 1.62<br>0 | "1"<br>"0" | VSIM<br>0.27 | V    | SIM reset<br>(output)                         |

|     |      | 3V SIM<br>Card       | 2.7<br>0  | "1"<br>"0" | VSIM<br>0.45 | V    |                                               |

| 3   | VCC  | 1.8V SIM<br>Card     | 1.6       | 1.8        | 2.0          | V    | Supply<br>voltage                             |

|     |      | 3V SIM<br>Card       | 2.8       | 3.0        | 3.2          | V    |                                               |

| 4   | GND  | GND                  | -         | 0          | -            | V    | Ground                                        |

| 5   | VCC  |                      | -         | -          | -            |      | Not con-<br>nected                            |

| 6   | I/O  | 1.8V Voh<br>1.8V Vol | 1.62<br>0 | "1"<br>"0" | VSIM<br>0.27 | V    | SIM data<br>(output)                          |

|     |      | 3 Voh<br>3 Vol       | 2.7<br>0  | "1"<br>"0" | VSIM<br>0.45 | V    |                                               |

|     |      | 1.8V Vih<br>1.8V Vil | 1.26<br>0 | "1"<br>"0" | VSIM<br>0.27 | V    | SIM data<br>(input)<br>Trise/Tfall<br>max 1us |

|     |      | 3V Vil<br>3V Vil     | 2.1<br>0  | "1"<br>"0" | VSIM<br>0.45 | V    |                                               |

## **Functional Description**

#### Modes of Operation

The NPM-8 baseband engine has five operating modes (in normal mode):

- Power\_off

- Acting Dead

- Active

- Sleep

- Charging

Additionally, two modes exist for product verification: testmode and local mode.

#### Power\_off

In this state, the phone is powered off, but supplied. VRTC regulator is active (enabled), having supply voltage from the main battery. Note, the RTC status in PWR\_OFF mode depends on whether RTC was enabled or not when entering PWR\_OFF. From Power\_off mode, UEM enters RESET mode (after a 20 ms delay), if any of following statements is

true (logical OR –function):

- Power\_on button detected (PWROFFX)

- Charger connection detected (VCHARDET)

- RTC\_ALARM detected

The phone enters POWER\_OFF mode from all the other modes except NO\_SUPPLY if the internal watchdog elapses.

#### Acting Dead

If the phone is off when the charger is connected, the phone is powered on but enters a state called Acting Dead. In this mode, no RF parts are powered. To the user, the phone acts as if it was switched off. A battery charging alert is given and/or a battery charging indication on the display is shown to acknowledge to the user that the battery is being charged.

#### Active

In the active mode, the phone is in normal operation — scanning for channels, listening to a base station, transmitting and processing information. There are several sub-states in the active mode, depending on whether the phone is in burst reception, burst transmission, the DSP is working, and so on.

In active mode, the RF regulators are controlled by the SW writing into UEM's registers wanted settings: VR1A/B must be kept disabled. VR2 can be enabled or forced into low quiescent current mode. VR3 is always enabled in active mode. VR4 -VR7 can be enabled, disabled, or forced into low quiescent current mode.

Table 20: Regulator controls

| Regulator | Notes                                                 |

|-----------|-------------------------------------------------------|

| VFLASH1   | Enabled; low Iq mode during sleep                     |

| VFLASH2   | Not used in NPM-8, must be kept disabled              |

| VANA      | Enabled; disabled in sleep mode                       |

| VIO       | Enabled; low lq mode during sleep                     |

| VCORE     | Enabled; low lq mode during sleep                     |

| VSIM      | Controlled by register writing                        |

| VR1A      | Not used in NPM-8, must be kept disabled              |

| VR1B      | Not used in NPM-8, must be kept disabled              |

| VR2       | Controlled by register writing; enabled in sleep mode |

| VR3       | Enabled; disabled in sleep mode                       |

| VR4       | Not used in NPM-8; must be kept disabled              |

| VR5       | Enabled; disabled in sleep mode                       |

| VR6       | Enabled; disabled in sleep mode                       |

Table 20: Regulator controls

| Regulator | Notes                                    |

|-----------|------------------------------------------|

| VR7       | Enabled; disabled in sleep mode          |

| IPA1-2    | Not used in NPM-8, must be kept disabled |

#### Sleep mode

Sleep mode is entered when both the MCU and DSP are in stand-by mode. Sleep is controlled by both processors. When SLEEPX low signal is detected, the UEM enters SLEEP mode. VCORE, VIO, and VFLASH1 regulators are put into low quiescent current mode. All RF regulators, except VR2, are disabled in SLEEP. When SLEEPX=1 is detected, the UEM enters ACTIVE mode and all functions are activated.

The sleep mode is exited either by the expiration of a sleep clock counter in the UEM or by some external interrupt, generated by a charger connection, key press, headset connection, etc.

In sleep mode, the main oscillator (26MHz) is shut down and the 32 kHz sleep clock oscillator is used as reference clock for the baseband.

#### Charging

Charging can be performed in parallel with any other operating mode. A BSI resistor inside the battery pack indicates the battery type/size. The resistor value corresponds to a specific battery capacity and technology.

The battery voltage, temperature, size, and current are measured by the UEM, controlled by the charging software running in the UPP.

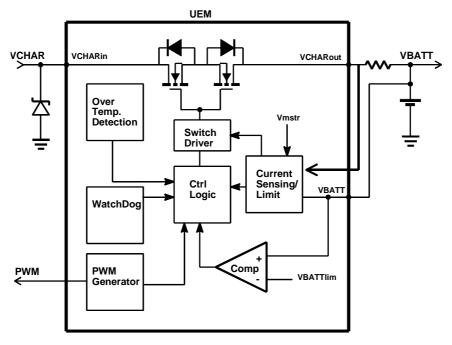

The charging control circuitry (CHACON) inside the UEM controls the charging current delivered from the charger to the battery. The battery voltage rise is limited by turning the UEM switch off when the battery voltage has reached VBATLim (programmable charging cut-off limits 3.6V / 5.0V / 5.25V). Charging current is monitored by measuring the voltage drop across a 220 mOhm resistor.

Charging is controlled by the UEM ASIC. The external components are mounted for EMC, reverse polarity and transient protection of the input to the baseband module. The charger connection is through the system connector interface. Both 2- and 3-wire type chargers are supported.

The operation of the charging circuit has been specified in such a way as to limit the power dissipation across the charge switch and to ensure safe operation in all modes.

Figure 2: UEM charging circuitry

#### **Charger Detection**

Connecting a charger creates voltage on VCHAR input of the UEM. When VCHAR input voltage level is detected to rise above VCH<sub>DET+</sub> threshold by UEM charging starts. VCHARDET signal is generated to indicate the presence of the charger for the SW.

The charger identification/acceptance is controlled by EM SW.

The charger recognition is initiated when the EM SW receives a "charger connected" interrupt. The algorithm basically consists of the following three steps:

- 1 Check that the charger output (voltage and current) is within safety limits.

- 2 Identify the charger.

- 3 Check that the charger is within the charger window.

If the charger is accepted and identified, the appropriate charging algorithm is initiated.

#### **Charge Control**

In active mode, charging is controlled by the digital portion of the UEM. Charging voltage and current monitoring is used to limit charge into a safe area. For that reason, UEM has programmable charging cut-off limits VBATLim<sub>1,2L,2H</sub> (3.6 V / 5.0 V / 5.25 V). Maximum charging current is limited to 1.2 A. Default for VBATLim is 3.6 V (used for initial charging of empty battery).

VBATLim<sub>1,2L,2H</sub> are designed with hysteresis. When the voltage rises above VBATLim<sub>1,2L,2H</sub>+ charging is stopped by turning charging switch OFF. No change in oper-

ational mode occurs. After voltage has decreased below VBATLim\_ charging restarts.

If VBAT is detected to rise above the programmed limit, the output signal OVV is set to '1' by CHACON. If charging current limit is reached, OVC output is set '1' by CHACON.

Pulse-width-Modulated (PWM) control signals PWM1 and PWM32 are generated by the digital portion of the UEM to CHACON block.

In principle, there are two PWM frequencies in use — depending on the type of the charger (standard charger 1 Hz, fast charger 32 Hz. Duty cycle range is 0% to 100%), but in NPM-8, only the 1 Hz mode will be used, as all charger will be treated as standard charges (2-wire types).

#### **Supported Chargers**

Supported chargers are:

- 2-wire chargers: ACP-7, ACP-8, and ACP-12.

- 3-wire chargers: PPH-1, ACP-9, ACT-1, LCH-8, and LCH-9.

The 3-wire chargers have a 3-wire interface to the phone (2 power and 1 control). The control wire carries the 32 Hz digital pulse width modulated signal, which must be generated by the phone to control the charger output voltage. In NPM-8, the 32Hz PWM for the charger is connected to GND inside the bottom connector. This sets full charger output voltage and equals 0% PWM from charger point of view.

#### **Charger Interface Protection**

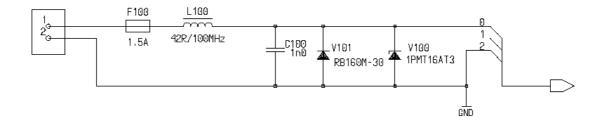

In order to ensure safe operation with all chargers and in misuse/fail situations, the charger interface is protected using transient voltage suppressor (TVS) and 1.5 A fuse. TVS used in NPM-8 is 16 V @ 175 W device. A Schottky diode is present to protect the charger input from reverse polarity chargers.

Figure 3: Charger interface

#### TVS characteristics:

Breakdown voltage ( $V_{BR}$ ) 17.8 Vmin (at  $I_T$  1.0mA)

Reverse standoff voltage ( $V_R$ ) 16 V Max reverse leakage current at  $V_R$  ( $I_R$ ) 5 uA

Max peak impulse current ( $I_{pp}$ ) 7 A (at Ta=25° C, current waveform: 10/1000us)

**NOKIA**

Max clamping voltage at  $I_{pp}$  ( $V_c$ )

26 V

## **Charging Circuitry Electrical Characteristics**

**Table 21: Electrical Characteristics**

| Parameter                                                                          |                                                                                                                                         | 311C3                                        | _                                           |                                              |                      |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------|

| Test conditions                                                                    | Symbol                                                                                                                                  | Min                                          | Тур                                         | Max                                          | Units                |

| Input voltage range (fast charger, no load)                                        | VCHAR                                                                                                                                   | 7.0                                          | 8.4                                         | 9.2                                          | V <sub>RMS</sub>     |

| Input voltage range (std charger, no load)                                         |                                                                                                                                         | -                                            | 11.1<br>7.9                                 | 16.9                                         | $V_{peak} \ V_{RMS}$ |

| Absolute Maximum VCHAR voltage                                                     |                                                                                                                                         | -0.3                                         | -                                           | +20                                          | ٧                    |

| Input resistance from VCharIn to ground                                            | Rin                                                                                                                                     | 2                                            | 4                                           | 6                                            | kΩ                   |

| Master reset threshold level                                                       | V <sub>MSTR+</sub><br>VMSTR-                                                                                                            | 2.0<br>1.8                                   | 2.1<br>1.9                                  | 2.2<br>2.0                                   | V                    |

| VCOFFX threshold levels                                                            | V <sub>COFF+</sub><br>VCOFF-                                                                                                            | 3.0<br>2.7                                   | 3.1<br>2.8                                  | 3.2<br>2.9                                   | V                    |

| VCHAR detection threshold level                                                    | VCH <sub>DET+</sub><br>VCHDET-                                                                                                          | 1.9<br>1.7                                   | 2.0<br>1.8                                  | 2.1<br>1.9                                   | V                    |

| Continuous input current (fast charger)                                            | I <sub>CH</sub>                                                                                                                         | -                                            | -                                           | 850                                          | mA                   |

| Maximum input current (std charger)                                                | I <sub>CH</sub>                                                                                                                         | -                                            | -                                           | 1.0                                          | A <sub>peak</sub>    |

| Start-up mode charging current                                                     | I <sub>START</sub>                                                                                                                      | 100                                          | -                                           | 150                                          | mA                   |

| PWM mode charge current                                                            | I <sub>LIM</sub>                                                                                                                        | 1.1                                          | 1.2                                         | 1.45                                         | Α                    |

| Output voltage (Battery voltage)                                                   | VBAT                                                                                                                                    | 0                                            | 3.6                                         | 4.2                                          | V                    |

| Charging cut-off limits (programmable)                                             | VBATLim <sub>1+</sub> VBATLim <sub>1-</sub> VBATLim <sub>2+</sub> VBATLim <sub>2</sub> - VBATLim <sub>2</sub> + VBATLim <sub>2</sub> H- | 3.54<br>3.32<br>4.85<br>4.65<br>5.10<br>4.90 | 3.65<br>3.50<br>5.0<br>4.85<br>5.25<br>5.10 | 3.76<br>3.66<br>5.15<br>5.05<br>5.40<br>5.30 | V                    |

| Charging switch resistance<br>(includes bonding and leads)<br>Temp =65°C (ambient) | R <sub>SW</sub>                                                                                                                         | -                                            | -                                           | 0.3                                          | W                    |

| PWM frequency (std charger)                                                        |                                                                                                                                         | 0.5                                          | 1                                           | 1.5                                          | Hz                   |

| PWM duty cycle                                                                     |                                                                                                                                         | 0                                            | -                                           | 100                                          | %                    |

| Switch output current slew rate                                                    | SR                                                                                                                                      | 0.4                                          | 0.6                                         | 0.8                                          | A/ms                 |

| Charging thermal shutdown threshold                                                | TjsdC+<br>TjsdC-                                                                                                                        | 140<br>120                                   | 150<br>130                                  | 160<br>140                                   | °C                   |

| VFLASH1 supply voltage input                                                       | VFLASH1                                                                                                                                 | 2.7                                          | 2.78                                        | 2.88                                         | ٧                    |

Note: VCHAR is used as a supply voltage for charging control parts.

NPM-8

#### Power Up and Reset

Power up and reset is controlled by the UEM ASIC. The NPM-8 baseband can be powered up in following ways:

- 1 Press power button, which means grounding the PWRONX pin of the UEM

- 2 Connect the charger to the charger input

- 3 Supply battery voltage to the battery pin

- 4 RTC Alarm, the RTC has been programmed to give an alarm

After receiving one of the above signals, the UEM counts a 20 ms delay and then enters its reset mode. The watchdog starts up and, if the battery voltage is greater than Vcoff+, a 200 ms delay is initiated to allow references, etc., to settle. After this delay elapses, the VFLASH1 regulator is enabled. Then, 500 us later, VR3, VANA, VIO, and VCORE are enabled. Finally, the PURX line is held low for 20 ms. This reset, PURX, is fed to the baseband ASIC UPP; resets are generated for the DSP and the MCU. During this reset phase, the UEM forces the VCXO regulator on, regardless of the status of the sleep control input signal to the UEM. All baseband regulators are switched on at the UEM power on, except for the SIM regulator that is controlled by the MCU. The UEM internal watchdog is running during the UEM reset state, with the longest watchdog time selected. If the watchdog expires, the UEM returns to power off state. The UEM watchdog is internally acknowledged at the rising edge of the PURX signal in order to always give the same watchdog response time to the MCU.

#### Power up with PWR key

When the power on key is pressed, the UEM enters the power up sequence as described in the *Power Up and Reset section*. Pressing the power key causes the PWRONX pin on the UEM to be grounded. The UEM PWRONX signal is not part of the keypad matrix. The power key is only connected to the UEM. This means that when the power key is pressed, an interrupt is generated to the UPP that starts the MCU. The MCU then reads the UEM interrupt register and notices that it is a PWRONX interrupt. The MCU now reads the status of the PWRONX signal using the UEM control bus, CBUS. If the PWRONX signal stays low for a specified time, the MCU accepts this as a valid power on state and continues with the SW initialization of the baseband. If the power on key does not indicate a valid power on situation, the MCU powers off the baseband.

#### Power up when charger is connected

In order to be able to detect and start charging in a case where the main battery is fully discharged (empty) and hence UEM has no supply (NO\_SUPPLY mode of UEM), charging is controlled by START-UP CHARGING circuitry.

Whenever VBAT level is detected to be below master reset threshold ( $V_{MSTR-}$ ), charging is controlled by START\_UP charge circuitry. Connecting a charger forces VCHAR input to rise above charger detection threshold, VCH<sub>DET+</sub>. By detection start-up charging is started. UEM generates 100mA constant output current from the connected charger's output voltage. As the battery charges, its voltage rises, and when the VBAT voltage level

is higher than the master reset threshold limit ( $V_{MSTR+}$ ) is detected and the START\_UP charge is terminated.

The charge control block (CHACON) monitors the VBAT voltage level. MSTRX='1' output reset signal (internal to UEM) is given to UEM's RESET block when VBAT>V<sub>MSTR+</sub> and the UEM enters into a reset sequence described in the *Power Up and Reset* section.

If VBAT is detected to fall below  $V_{MSTR-}$  during start-up charging, charging is cancelled. It will restart if new rising edge on VCHAR input is detected (VCHAR rising above VCH<sub>DFT+</sub>).

#### Power up when battery is connected

Baseband can be powered up by connecting a battery with sufficient voltage. Battery voltage has to be higher than the UEM internal comparator threshold level,  $V_{coff+}$ . When battery proper voltage is detected, the UEM enters the reset sequence as described in the *Power Up and Reset* section. This power up sequence is meant for test purposes; in normal use (Btemp resistor >  $1k\Omega$ ) the phone will power off again immediately, without noticing the user.

#### RTC alarm power up

If the phone is in POWER\_OFF mode when RTC alarm occurs, the wake up procedure is as described in the *Power Up and Reset* section. After the baseband is powered on, an interrupt is given to MCU. When the RTC alarm occurs during ACTIVE mode, the interrupt for MCU is generated.

#### A/D Channels

The UEM contains the following A/D converter channels that are used for several measurement purposes. The general slow A/D converter is a 10-bit converter using the UEM interface clock for the conversion. An interrupt will be given at the end of the measurement.

The UEM's 11-channel analog-to-digital converter is used to monitor charging functions, battery functions, voltage levels in external accessory detection inputs, user interface, and RF functions.

When the conversion begins, the converter input is selected. Then the signal processing block creates a data with MSB set to '1' and others to '0'. In the D/A converter, this data controls the switches, which connect the input reference voltage (VrefADC) to the resistor network. The generated output voltage is compared with the input voltage under measurement and if the latter is greater, MSB remains '1' else it is set '0'. The following step is used to test the next bit and the next, until LSB is reached. The result is then stored to the ADCR register for the UPP to read.

The monitored battery functions are battery voltage (VBATADC), battery type (BSI), and battery temperature (BTEMP) indication.

The battery type is recognized through a resistive voltage divider. In the phone there is a

100 kOhm pull up resistor in the BSI line and the battery has a pull-down resistor in the same line. Depending on the battery type, the pull-down resistor value is changed. The battery temperature is measured equivalently, except that the battery has a NTC pull-down resistor in the BTEMP line.

KEYB1&2 inputs are made for keyboard scanning purposes. These inputs are also routed internally to the miscellaneous block. KEYB1&2 inputs are not used In NPM-8, and the connected interrupts must be kept disabled by the SW.

The HEADINT and HOOKINT are external accessory detection inputs used for monitoring voltage levels in these inputs. They are routed internally from the miscellanous block and they are connected to the converter through a 2:1 multiplexer.

PATEMP and VCXOTEMP channels are not used as originally intended. PATEMP input is used for the detection of accessory covers (CTI). VCXOTEMP is not used in NPM-8.

| Characteristics           | Min | Тур | Max     | Unit |

|---------------------------|-----|-----|---------|------|

| Number of bits            | 10  |     |         | bits |

| Integral nonlinearity     | -   | -   | +/- 2   | LSB  |

| Differential nonlinearity | -   | -   | +/- 2.5 | LSB  |

| Conversion time           | -   | -   | 11      | μs   |

| Input voltage range (1)   | 0   | -   | 2.7     | V    |

| Input capacitance         | 4   | 5   | 6       | pF   |

Table 22: Slow A/D converter characteristics

Table 23: Slow A/D converter input ranges

| Signal   | Min     | Тур | Max           | Unit | Notes                             |

|----------|---------|-----|---------------|------|-----------------------------------|

| VBATADC  | 2.7     | -   | 5.25          | V    | Physical input on UEM is VBATREGS |

| ICHAR    | VBATADC | -   | VBATADC+0.316 | V    |                                   |

| VCHARADC | 0.1     | -   | 1.35          | V    |                                   |

| BSI      | 0       | -   | 2.7           | V    |                                   |

| ВТЕМР    | 0       | -   | 2.7           | V    |                                   |

| PATEMP   | 0       | -   | 2.7           | V    | Used for CTI                      |

| VCXOTEMP | 0       | -   | 2.7           | V    | Not used in NPM-8                 |

| HEADINT  | 0       | -   | 2.7           | V    |                                   |

| HOOKINT  | 0       | -   | 2.7           | V    |                                   |

| LS       | 0       | -   | 2.7           | V    | Not used in NPM-8                 |

| KEYB1    | 0       | -   | 2.7           | V    | Not used in NPM-8                 |

<sup>(1)</sup> AD converter is calibrated in production.

Table 23: Slow A/D converter input ranges

| Signal | Min | Тур | Max | Unit | Notes             |

|--------|-----|-----|-----|------|-------------------|

| KEYB2  | 0   | -   | 2.7 | V    | Not used in NPM-8 |

AD converter is calibrated in production.

#### Battery Voltage Measurement A/D Channel (VBATADC)

The battery voltage is scaled inside the UEM in order to avoid external components. The maximum battery voltage that gives a full A/D reading is 5.25 V.

Battery voltage can be connected to sample-and-hold circuit either through a resistive voltage divider or through a voltage-scaling circuit. The voltage-scaling circuit is used to get larger input voltage range for the converter than what is achieved with the resistive divider. The sample-and-hold circuit is used to measure the battery voltage during transmit burst. Otherwise, the S/H circuit is bypassed. Note that both the battery voltage (VBATADC) and the charger voltage (VCHARADC) are sampled whenever the sampling function is used.

#### Charger Voltage Measurement A/D Channel (VCHARADC)

This channel is used to measure the charger input voltage VCHAR. The charger input idle voltage is measured to identify the charger. Associated with the charger voltage measurement, an envelope detector is used to detect a rectifier bridge type of charger. Connection of the charger is performed by the rising edge of the charger input. The charger must be a full-wave rectifier. A half-wave rectifier charger has to be rejected.

This A/D channel has a built-in feature built that allows the charger voltage measurement to be specified to be performed whether the charger switch is closed or open. This information is provided by the MCU when this channel is addressed.

The charger measurement A/D channel can also be timed to the charger envelop detector in order to measure the standard charger peak voltage.

#### Charger Current Measurement A/D Channel (ICHAR)

This A/D channel is used to measure the charger current ICHAR. The current sensor is implemented using a  $0.22\Omega$  resistor in series between the UEM charging voltage output and the battery voltage. The voltage drop over the resistor is examined. The charger current measurement is used for charger detection and maintenance charging PWM calculations.

#### Battery Temperature Measurement A/D Channel (BTEMP)

The temperature of the battery pack is monitored during charging. The battery pack is equipped with an NTC resistor (value is 47 kOhm at 25° C). The BTEMP signal is connected on the baseband to the UEM. An external 100 kOhm pull-up is needed.

<sup>(1)</sup> AD converter is calibrated in production.

#### Battery Size Measurement A/D Channel (BSI)

This channel is used to identify the battery. The battery pack BLC-2 has a resistor 75kOhm connected to ground. An external 100kOhm pull-up resistor is on the phone side. The BSI signal is connected to the UEM.

#### External Accessory Detection A/D Channel (HEADINT, HOOKINT)

An A/D converter channel is used to detect DCT4-type accessories. An A/D converter channel is used to measure the DC level on the external microphone. The detection is implemented using a pull-down resistor in the accessory and a pull-up on the baseband side. The pull-up resistor on the baseband side is internal to the UEM. This A/D channel is internally connected to either HeadInt or HookInt.

#### PA Temperature measurement A/D Channel (PATEMP)

In NPM-8, this A/D channel is used for Cover Type Detection (CTI) in conjunction with DC-OUT covers. The detection is implemented using a pull-down resistor in the accessory and a pull-up on the baseband side.

#### LCD & Keyboard Backlight

#### LCD Backlight

The LCD Backlight consists of two TBSF (Through the Board Side Firing) yellow/green LEDs, which are placed on the main PWB below the LCD area. They light into the light guide where the light is distributed to generate sufficient backlight for the LCD.

#### Keyboard light

The keyboard light consists of two TBSF yellow/green LEDs, which are placed under the keyboard and use the light guide to distribute the light.

#### LED driver circuit

The LED drivers for the LCD & Keyboard backlight are shared as shown in the following figure. The driver circuit is controlled by the UEM output pin [DLIGHT] and drive current is 15 mA per LED. By using appropriate SW, the driver can be PWM-controlled for dimming purposes.

Figure 4: Shared LED driver circuit for LCD and Keyboard backlight UTDRV(5:0)

LCD cell

The LCD is a black-and-white 96x65 full dot matrix display. The LCD has a standard DCT4

interface. The LCD interface between the LCD cell and the main PWB can be viewed in the *LCD* section. The LCD cell is part of the complete LCD module, which includes metal frame, gasket, light guide, spring connector, transflector, dome sheet, and earpiece.

The LCD is powered from both  $V_{FLASH1}$  and  $V_{IO}$ .  $V_{FLASH1}$  is used for the boosting circuit and  $V_{IO}$  for the driver chip.

#### SIM Interface

The UEM contains the SIM interface logic level shifting. The SIM supports 3 V and 1.8 V SIMs. SIM supply voltage is selected by a register in the UEM. It is only allowed to change the SIM supply voltage when the SIM IF is initialized.

The SIM power up/down sequence is generated in the UEM. This means that the UEM generates the RST signal to the SIM. Also the SIMCardDet signal is connected to the UEM. The card detection is taken from the BSI signal, which detects the removal of the battery. The monitoring of the BSI signal is done by a comparator inside the UEM. The comparator offset is such that the comparator output does not alter the state as long as the battery is connected. The threshold voltage is calculated from the battery size specifications.

The SIM interface is powered up when the SIMCardDet signal indicates "card in". This signal is derived from the BSI signal.

| Parameter                                | Variable | Min  | Тур | Max  | Unit |

|------------------------------------------|----------|------|-----|------|------|

| BSI comparator threshold                 | Vkey     | 1.94 | 2.1 | 2.26 | V    |

| BSI comparator hysteresis <sup>(1)</sup> | Vsimhyst | 50   | 75  | 100  | mV   |

Table 24: BSI Detection

The SIM interface is located in the two ASICs: UPP and UEM.

The SIM interface in the UEM contains power up/down, port gating, card detect, data receiving, ATR-counter, registers, and level-shifting buffers logic. The SIM interface is the electrical interface between the Subscriber Identity Module Card (SIM Card) and mobile phone (via the UEM device).

The data communication between the card and the phone is asynchronous half-duplex. The clock supplied to the card is 3.25MHz. The data baud rate is SIM card clock frequency divided by 372 (by default), 64, 32, or 16. The protocol type that is supported is T=0 (asynchronous half-duplex character transmission as defined in ISO 7816-3).

The internal clock frequency from the UPP CTSI block is 13MHz in GSM. To achieve the minimum starting SIMCardClk rate of 3.25 MHz (as is required by the authentication procedure) and the duty cycle requirement of between 40% and 60%, the slowest possible clock supplied to the SIM has to be in the GSM system clock rate of 13/4MHz.

<sup>(1)</sup> Hysteresis is defined as [Vkey(+)-Vkey(-)] / 2

#### Internal Audio

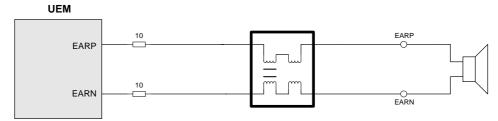

#### Earpiece

The earpiece selected for NPM-8 is the standard DCT3 13-mm earpiece. The earpiece design is leak-tolerant.

The internal earpiece is a dynamic earpiece with an impedance of  $32\Omega$ . The earpiece is a low-impedance type, since the sound pressure is to be generated using current and not voltage (supply voltage is restricted to 2.7 V). The earpiece is driven directly by the UEM; the earpiece driver in the UEM is a bridge amplifier.

Figure 5: Speaker Interface

#### Internal Microphone

NPM-8 uses an omnidirectional microphone that is located in the system connector, sealed in a rubber gasket.

The microphone is biased from the UEM MICB1 output and lowpass filtered through an RC filter (470\_,22uF) giving 20 dB attenuation at 217 Hz. The signal path from the microphone is lowpass filtered (2.2k\_,1nF) and EMC decoupled (22pF)

The two 33nF capacitors are used to create a 1st order high-pass filter. The input impedance of the gain stage at MIC1P/N is the other part of the RC circuit. The high-pass filter is required due to low-frequency noise, which is one phenomenon identified as a problem when the internal microphone is used as handsfree microphone (PPH-1/carkit mode).

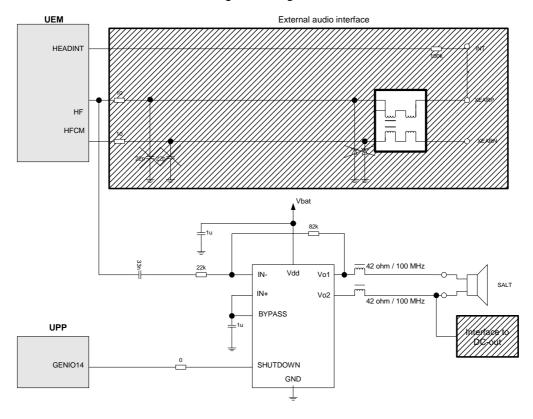

#### Ringer

A 13 mm speaker is used to generate alerting tones and melodies to indicate incoming calls, as well as used to generate game sound, keypress, and warning tones for the user.

Alerting tones and MIDI melodies are generated by the speaker, which is controlled by a sine driven output from the UEM and an external amplifier.

The speaker is electrically connected to the PWB by spring contacts (similar to that for the internal earpiece).

3. System Module

Figure 6: Ringer interface

#### Accessories

NPM-8 supports Li-ion and NiMH batteries, "footprint" "C" from the DCT4 Lion/Janette battery program.

| Signal name | Pin number | Function                                                                                 |

|-------------|------------|------------------------------------------------------------------------------------------|

| VBAT        | 1          | Positive battery terminal                                                                |

| BSI         | 2          | Battery capacity measurement (fixed resistor, connected to GND, inside the battery pack) |

| ВТЕМР       | 3          | Battery temperature measurement (measured by ntc resistor connected to GND inside pack)  |

| GND         | 4          | Negative/common battery terminal                                                         |

The BSI fixed resistor value indicates the type and default capacity of a battery; NTC resistor BTEMP measures the battery temperature.

Temperature and capacity information are needed for charge control. These resistors are connected to the BSI and BTEMP pins of the battery connector. The P\phone has 100 k $\Omega$  pull-up resistors for these lines so that they can be read by A/D inputs in the phone.

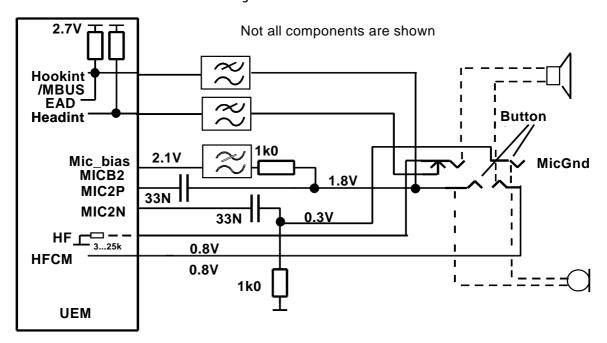

#### **External Audio**

NPM-8 supports fully differential external audio accessory connection. A headset and PPH-1 can be directly connected to the system connector. Detection of the different

accessories is made in analog by reading the DC voltage value of the EAD converter.

Figure 7: Headset interface

#### **Analog Audio Accessory Detection**

The accessory is detected by the HeadInt signal when the plug is inserted. Normally when no plug is present, the internal pull-down on the HF pin pulls down the HeadInt signal. HeadInt comparator value is 1.9 V. When the plug is inserted, the switch in the connector is opened and the HeadInt signal is pulled up by the internal pull-up. The 1.9 V threshold level is reached and the comparator output changes to low state, causing an interrupt. The reverse is true when the accessory is disconnected: the HeadInt switch is closed and the HeadInt is pulled down.

|                                   | HookInt | HeadInt |

|-----------------------------------|---------|---------|

| Basic Headset, fully differential | Н       | Н       |

| Button Headset (Switch closed)    | L       | Н       |

| Button Headset (Switch open)      | Н       | Н       |

| PPH-1                             | Н       | Н       |

| No accessory                      | Н       | L       |

Table 25: Truth table for HookInt and HeadInt

HeadInt signal is used to detect when the accessory is connected.

HookInt signal is used to detect when the button of the headset is pressed.

NOTE: Charging must be disabled during identification of PPH-1.

#### **Headset Detection**